电机的应用越来越普遍,对方式的要求也不断提高。本文利用ALTERA公司最新开发的SOPC解决方案,提出了基于NiosII软核处理器的

代码生成功能模块IP核。IP核的生成,不仅方便设计者灵活使用,节省资源,也大大缩短了设计周期。设计者可以根据需要直接调用IP核来组成NiosII系统,然后将此系统下载到FPGA中实现。IP核不仅可以用在

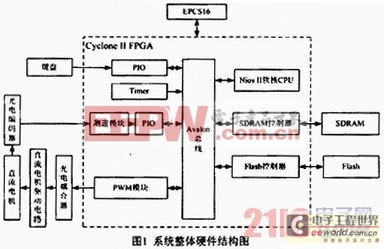

如图1所示,系统整体由FPGA芯片控制,其控制核心为ALTERA公司的NiosII软核CPU,本文将着重介绍图中两个控制功能模块PWM模块和测速模块的设计与生成。这两个控制功能模块均采用VHDL硬件描述语言自行设计生成可以调用的IP核,通过QuartusII对其进行编译、仿真验证其正确性,最后将生成自定义接口功能模块添加到顶层原理图中,完成整个调速系统的设计。

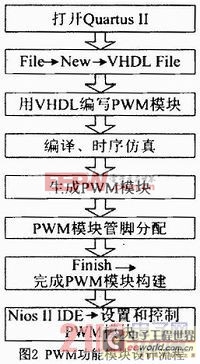

PWM模块利用直流电机占空比来控制电机电枢电压,从而控制直流电机的转速。设计过程如图2所示。

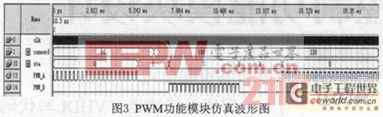

从图3可以看出,仿真时给定一个时钟信号Clk,Sta用来控制直流电机正反转,图3中的0表示直流电机处于正转状态,1表示停止,3表示反转;Conword为占空比信号,仿线%三种值;PWM A表示直流电机处于正转状态时的占空比输出,这时PWM B的输出为0;PWM B表示直流电机处于反转时的占空比输出,此时PWM A的输出值为0;而当电机处于停止状态时,如图中当Sta值为1时,PWM A和PWM B的输出值均为0。经仿真时序图验证此设计是有效的,从而将其生成PWM功能模块。

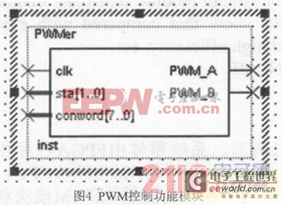

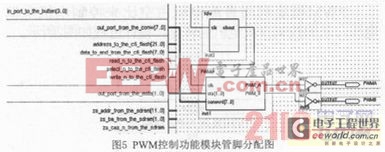

PWM控制功能模块的原理如下:将时钟源50MHz的基频信号64分频,作为PWM模块的基频信号,以256个该基频脉冲信号作为PWM输出的一个周期,由NiosII处理器给出Conword的值指定一个PWM周期内高电平持续时间,改变Conword的值即刻改变占空比输出的值。Sta用来控制电机正反转。

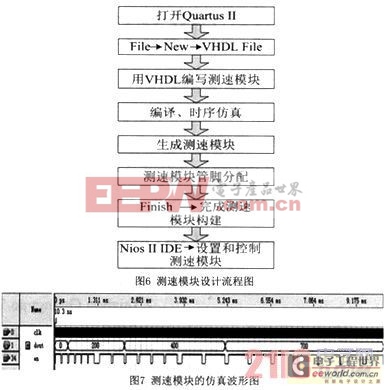

测速模块的作用主要是利用基频的周期来计算光栅信号的周期,算出直流电机的转速。其设计的流程图如图6所示。

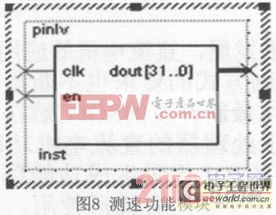

测速模块的时序仿线中可以看出,仿真时给定一个时钟信号Clk用于计时,en为使能信号,即表示光栅有效,dout表示光栅有效时间,仿线三种值。通过时序仿真验证了此设计的测速模块是有效的,从而将其生成测速功能模块。

其工作原理如下:给出己知频率的基频,用光栅作为门限,测基频脉冲的个数,由基频的周期来计算光栅信号的周期,再算出转速,

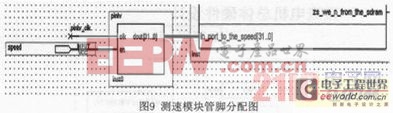

电机控制算法即根据测速模块测出的速度进行算法调整,达到闭环控制的效果。测速模块的管脚分配图如图9所示。

VHDL语言设计了PWM功能模块和测速模块,并进行了仿真,验证了设计的正确性,完成了系统设计。本文的创新之处在于利用软硬件直接设计控制功能模块,这种设计具有开发周期短、通用能力好、易于开发扩展等优点,值得推广。